Intel Reiterates Plans to Merge CPU, GPU High-performance Chip Roadmaps

Intel reiterated it is well on its way to merging its roadmap of high-performance CPUs and GPUs as it shifts over to newer manufacturing processes and packaging technologies in the coming years.

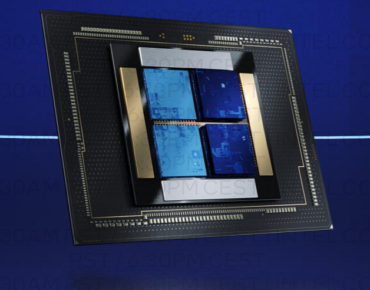

The company is merging the CPU and GPU lineups into a chip (codenamed Falcon Shores) which Intel has dubbed an XPU. Falcon Shores is a “bigger architectural” change that brings together x86 and Xe graphics cores into a single package, said Jeff McVeigh, vice president and general manager of the Super Compute Group at Intel, during a briefing with the press ahead of the ISC High Performance supercomputing conference.

Intel earlier this year presented a roadmap with Falcon Shores coming later in 2024, and said it would deliver significant improvements in bandwidth, performance-per-watt, compute density and memory capacity.

The Falcon Shores architecture will use a chiplet approach, in which multiple dies and different processor modules made on different manufacturing processes can be crammed tightly in a single chip package. That gives Intel a higher level of customization on the types of CPUs, GPUs, I/O, memory types, power management and other circuits it can put in its chips.

Falcon Shores provides “sort of all the benefits of having those closely coupled tiles right next to each other on a single package,” McVeigh said, adding, “The chip will be able to deliver through the advanced packaging, the IO capabilities, the shared memory and having a single programming model across those components.”

However, it is not yet customizable to a level that customers may want, McVeigh said.

“It’s not like you design your own XPU and we will produce it. We’ll have set versions of that. But it allows us the flexibility much later in the design process based on the workloads the market demands, if there’s some new technologies like how AI has become so popular over the last five years, as new trends come along, we can more easily adapt and place those within the design,” McVeigh said.

Falcon Shores will have a more “CPU like” programming model with a shared memory environment, McVeigh said.

“You’re not having to kind of deal with all the offload characteristics and latency associated when you have with discrete GPU over PCI Express,” McVeigh said.

Falcon Shores is still two CPU and GPU chip upgrades away. In the second half of this year, the company will ship Xeon chips codenamed Sapphire Rapids and Sapphire Rapids with HBM. Later this year, the company will also ship a supercomputing GPU codenamed Ponte Vecchio, targeted at AI and high-performance computing markets.

Ponte Vecchio will be followed by a successor codenamed Rialto Bridge, which will be slot upgradable. Rialto Bridge will be an incremental architectural upgrade and will pack in more Xe graphics cores. Intel is targeting a 30 percent performance upgrade with certain workloads, McVeigh said.

McVeigh said Falcon Shores will be a “tick” upgrade in the company’s “tick tock” chip development cycle, meaning it will feature brand new architecture with new technologies. Intel will employ an advanced manufacturing process and packaging technologies to support Falcon Shores’ chiplet design.

Falcon Shores also represents a step ahead in Intel’s march to exascale performance with Ponte Vecchio, and ultimately to zettascale computing. The company is going to integrate optical I/O in such chips to address bandwidth and energy efficiency, and that could be part of GPUs and also the Falcon Shore XPU.

McVeigh also touched on other HPC topics, including memory hierarchies, and performance and energy efficiencies achieved with its bitcoin chip codenamed Bonanza Mine, which is an example of low-voltage clocking schemes that will be required in high-performance computing environments.